# 2048-pixel CCD Linear Sensor (B/W)

## **Description**

The ILX551B is a reduction type CCD linear sensor designed for facsimile, image scanner and OCR use. This sensor reads B4 size documents at a density of 200DPI (Dot Per Inch). A built-in timing generator and clock-drivers ensure direct drive at 5V logic for easy use.

#### **Features**

- Number of effective pixels: 2048 pixels

Pixel size: 14µm × 14µm (14µm pitch)

- Built-in timing generator and clock-drivers

- Ultra low lag

- Maximum clock frequency: 5MHz

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul> | $V_{DD1}$ | 11         | V  |

|------------------------------------|-----------|------------|----|

|                                    | $V_{DD2}$ | 6          | V  |

| • Operating temperature            |           | -10 to +55 | °C |

| Storage temperature                |           | -30 to +80 | °C |

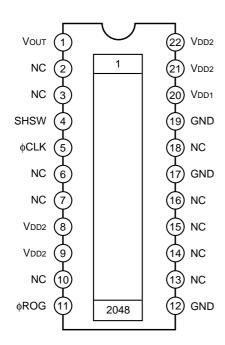

#### Pin Configuration (Top View)

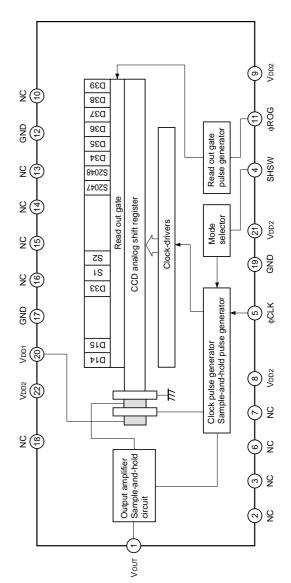

## **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

## **Pin Description**

| Pin No. | Symbol           | Description                                                                                                                      | Pin No. | Symbol           | Description     |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------|---------|------------------|-----------------|

| 1       | Vouт             | Signal output                                                                                                                    | 12      | GND              | GND             |

| 2       | NC               | NC                                                                                                                               | 13      | NC               | NC              |

| 3       | NC               | NC                                                                                                                               | 14      | NC               | NC              |

| 4       | SHSW             | Switch $\{ \begin{array}{l} \mbox{With S/H} \rightarrow \mbox{GND} \\ \mbox{Without S/H} \rightarrow \mbox{Vdd2} \end{array} \}$ | 15      | NC               | NC              |

| 5       | φCLK             | Clock pulse                                                                                                                      | 16      | NC               | NC              |

| 6       | NC               | NC                                                                                                                               | 17      | GND              | GND             |

| 7       | NC               | NC                                                                                                                               | 18      | NC               | NC              |

| 8       | V <sub>DD2</sub> | 5V power supply                                                                                                                  | 19      | GND              | GND             |

| 9       | V <sub>DD2</sub> | 5V power supply                                                                                                                  | 20      | V <sub>DD1</sub> | 9V power supply |

| 10      | NC               | NC                                                                                                                               | 21      | V <sub>DD2</sub> | 5V power supply |

| 11      | φROG             | Clock pulse                                                                                                                      | 22      | V <sub>DD2</sub> | 5V power supply |

## **Recommended Supply voltage**

| Item             | Min. | Тур. | Max. | Unit |

|------------------|------|------|------|------|

| V <sub>DD1</sub> | 8.5  | 9.0  | 9.5  | ٧    |

| V <sub>DD2</sub> | 4.75 | 5.0  | 5.25 | V    |

Note) Rules for raising and lowering power supply voltage

To raise power supply voltage, first raise VDD1 (9V) and then VDD2 (5V).

To lower voltage, first lower VDD2 (5V) and then VDD1 (9V).

## **Mode Description**

| Mode in use | Pin condition    |

|-------------|------------------|

| S/H         | Pin 4 SHSW       |

| Yes         | GND              |

| No          | V <sub>DD2</sub> |

## **Input Capacity of Pins**

| Item              | Symbol | Min. | Тур. | Max. | Unit |

|-------------------|--------|------|------|------|------|

| Input capacity of | Сфськ  | _    | 10   | _    | pF   |

| Input capacity of | Сфкоб  | _    | 10   |      | pF   |

## **Recommended Input Pulse Voltage**

| Item                   | Min. | Тур. | Max. | Unit |

|------------------------|------|------|------|------|

| Input clock high level | 4.5  | 5.0  | 5.5  | V    |

| Input clock low level  | 0    |      | 0.5  | V    |

#### **Electro-optical Characteristics**

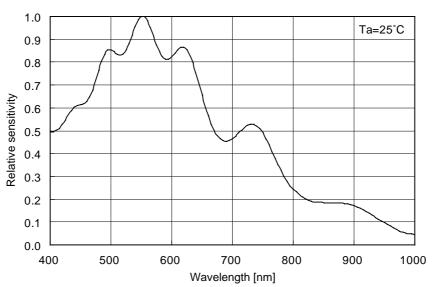

(Ta = 25°C, VDD1 = 9V, VDD2 = 5V, Clock frequency = 1MHz, Light source = 3200K, IR cut filter: CM-500S (t = 1.0mm))

| Item                      | Symbol | Min. | Тур.  | Max. | Unit       | Remarks |

|---------------------------|--------|------|-------|------|------------|---------|

| Sensitivity               | R      | 30   | 40    | 50   | V/(lx · s) | Note 1  |

| Sensitivity nonuniformity | PRNU   | _    | 2.0   | 8.0  | %          | Note 2  |

| Saturation output voltage | VSAT   | 1.5  | 1.8   | _    | V          |         |

| Dark voltage average      | Vdrk   | _    | 0.3   | 2.0  | mV         | Note 3  |

| Dark signal nonuniformity | DSNU   | _    | 0.5   | 3.0  | mV         | Note 3  |

| Image lag                 | IL     | _    | 0.02  | _    | %          | Note 4  |

| Dynamic range             | DR     | _    | 6000  | _    | _          | Note 5  |

| Saturation exposure       | SE     | _    | 0.045 | _    | lx·s       | Note 6  |

| 9V supply current         | IVDD1  | _    | 4.0   | 8.0  | mA         |         |

| 5V supply current         | IVDD2  | _    | 1.8   | 5.0  | mA         | _       |

| Total transfer efficiency | TTE    | 92.0 | 97.0  | _    | %          |         |

| Output impedance          | Zo     | _    | 600   | _    | Ω          | _       |

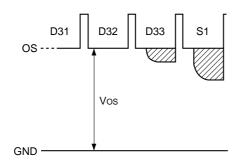

| Offset level              | Vos    | _    | 4.0   | _    | V          | Note 7  |

## Note)

- 1. For the sensitivity test light is applied with a uniform intensity of illumination.

- 2. PRNU is defined as indicated below. Ray incidence conditions are the same as for Note 1.

$$PRNU = \frac{(V_{MAX} - V_{MIN})/2}{V_{AVF}} \times 100 [\%]$$

The maximum output is set to VMAX, the minimum output to VMIN and the average output to VAVE.

- 3. Integration time is 10ms.

- 4. Vout = 500mV

5. DR =

$$\frac{V_{SAT}}{V_{DRK}}$$

When optical accumulated time is shorter, the dynamic range gets wider because dark voltage is in proportion to optical accumulated time.

6. SE =

$$\frac{V_{SAT}}{R}$$

7. Vos is defined as indicated below.

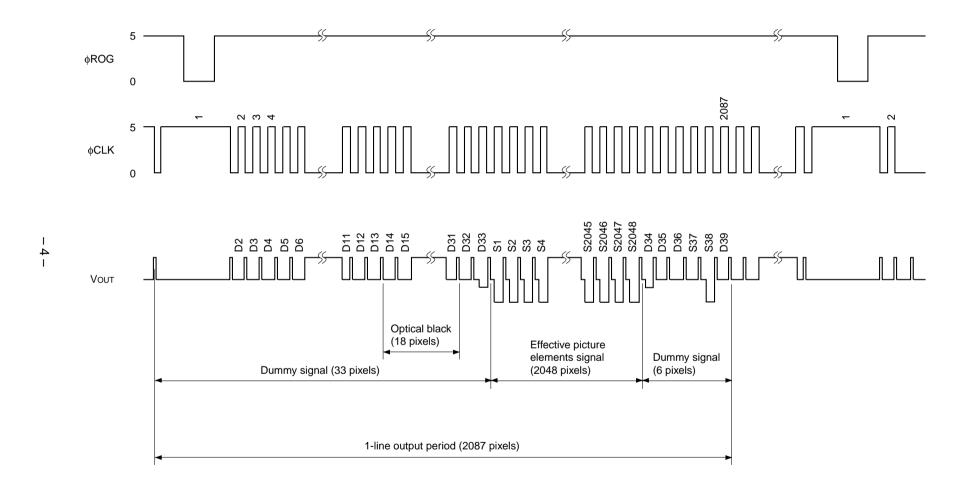

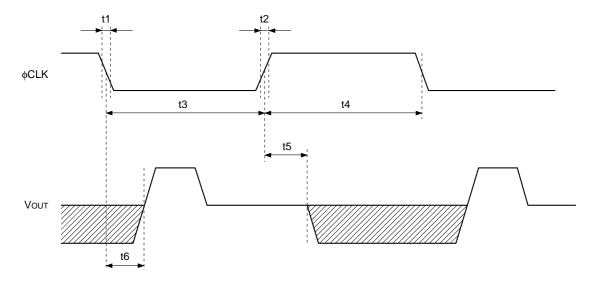

Fig.1. Clock Timing Diagram (without S/H mode)

| Item                      | Symbol | Min. | Тур. | Max. | Unit |

|---------------------------|--------|------|------|------|------|

| φCLK pulse rise/fall time | t1, t2 | 0    | 10   | _    | ns   |

| φCLK pulse duty*1         | _      | 40   | 50   | 60   | %    |

| фCLK – Vouт1              | t5     | 50   | 80   | 110  | ns   |

| фCLK – Vouт2              | t6     | 30   | 75   | 120  | ns   |

<sup>\*1</sup>  $100 \times t3$  / (t3 + t4)

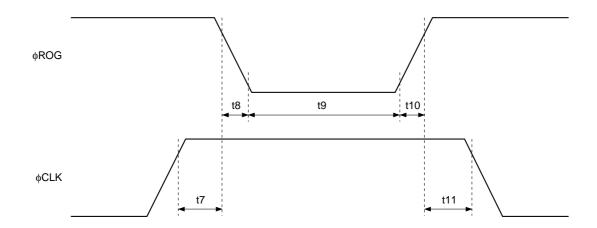

Fig. 3.  $\phi$ ROG,  $\phi$ CLK Timing

| Item                      | Symbol  | Min. | Тур. | Max. | Unit |

|---------------------------|---------|------|------|------|------|

| φROG, φCLK pulse timing   | t7, t11 | 500  | 1000 |      | ns   |

| φROG pulse rise/fall time | t8, t10 | 0    | 10   | _    | ns   |

| φROG pulse period         | t9      | 500  | 1000 | _    | ns   |

## **Example of Representative Characteristics**

Dark signal voltage rate vs. Ambient temperature (Standard characteristics)

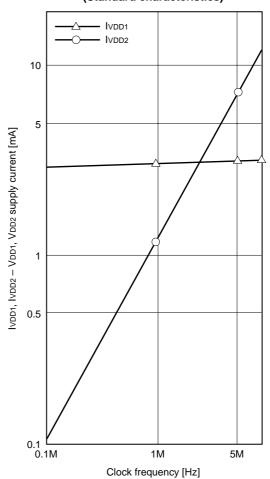

VDD1, VDD2 supply current vs. Clock frequency (Standard characteristics)

#### **Notes on Handling**

1) Static charge prevention

CCD image sensors are easily damaged by static discharge. Before handling, be sure to take the following protective measures.

- a) Either handle bare handed or use non-chargeable gloves, clothes or material. Also use conductive shoes.

- b) When handling directly use an eath band.

- c) Install a conductive mat on the floor or working table to prevent the generation of static electricity.

- d) lonized air is recommended for discharge when handling CCD image sensors.

- e) For the shipment of mounted substrates use cartons treated for the prevention of static charges.

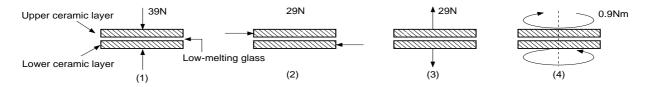

#### 2) Notes on handling CCD Cer-DIP package

The following points should be observed when handling and installing Cer-DIP packages.

- a) Remain within the following limits when applying static load to the ceramic portion of the package:

- Compressive strength: 39N/surface

(Do not apply load more than 0.7mm inside the outer perimeter of the glass portion.)

(2) Shearing strength: 29N/surface

(3) Tensile strength: 29N/surface

(4) Torsional strength: 0.9Nm

- b) In addition, if a load is applied to the entire surface by a hard component, bending stress may be generated and the package may fracture, etc., depending on the flatness of the ceramic portion. Therefore, for installation, either use an elastic load, such as a spring plate, or an adhesive.

- c) Be aware that any of the following can cause the glass to crack because the upper and lower ceramic layers are shielded by low-melting glass.

- (1) Applying repetitive bending stress to the external leads.

- (2) Applying heat to the external leads for an extended period of time with a soldering iron.

- (3) Rapid cooling or heating.

- (4) Rapid cooling or impact to a limited portion of the low-melting glass with a small-tipped tool such as tweezers.

- (5) Prying the upper or lower ceramic layers away at a support point of the low-melting glass. Note that the preceding notes should also be observed when removing a component from a board after it has already been soldered.

#### 3) Soldering

- a) Make sure the package temperature does not exceed 80°C.

- b) Solder dipping in a mounting furnace causes demage to the glass abd other defects. Use a 30W soldering iron with a ground wire and solder each pin in less than 2 seconds. For repairs and remount, cool sufficiently.

- c) To dismount image sensors, do not use a solder suction equipment. When using an electric desoldering tool, ground the controller. For the control system, use a zero cross type.

- 4) Dust and dirt protection

- a) Operate in clean environments.

- b) Do not either touch glass plates by hand or have any object come in contact with glass surfaces. Should dirt stick to a glass surface blow it off with an air blower. (For dirt stuck through static electricity, ionized air is recommended.)

- c) Clean with a cotton bud and ethyl alcohol if the glass surface is grease stained. Be careful not to scratch the glass.

- d) Keep in case to protect from dust and dirt. To prevent dew condensation, preheat or precool when moving to a room with great temperature differences.

- 5) Exposure to high temperature or humidity will affect the characteristics. Accordingly avoid storage or usage in such conditions.

- 6) CCD image sensors are precise optical equipment that should not be subject to mechanical shocks.

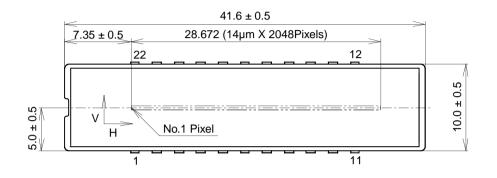

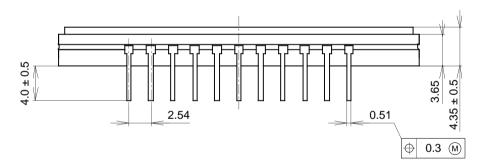

# 22 pin DIP (400mil)

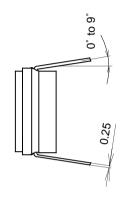

- 1. The height from the bottom to the sensor surface is  $2.45 \pm 0.3$ mm.

- 2. The thickness of the cover glass is 0.7mm, and the refractive index is 1.5.

## PACKAGE STRUCTURE

| PACKAGE MATERIAL | Cer-DIP      |

|------------------|--------------|

| LEAD TREATMENT   | TIN PLATING  |

| LEAD MATERIAL    | 42 ALLOY     |

| PACKAGE MASS     | 5.20g        |

| DRAWING NUMBER   | LS-A18-01(E) |

- 10*-*